Introducing the AQR113C solution-based 10 Gigabit SFP Module compatible with multiple rates

Time: 2023-07-14

This article introduces the rate compatibility of the host interface and network cable interface of the 10GbE SFP module based on Marvell AQR113C program.

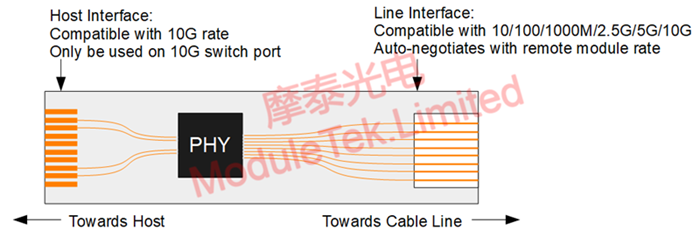

1. Host Interface

The host interface of AQR113C based 10GbE SFP module is set to 10G XFI mode, and the rate of the host interface is not adaptable to other rates, so the 10GbE interface of this solution can only be used on the switch port that has been set to 10G rate beforehand, or it will not work properly.

2. Network cable interface

When the 10GbE SFP module of AQR113C is interconnected with the other module, it can be compatible with 10/100/1000M/2.5G/5G/10G, and the rate will be automatically adjusted according to the rate of the port on the other end. When the port rate of the other end is fixed 10G, it will adapt to 10G, when the port rate of the other end is fixed 1G, it will adapt to 1G, and other rates are similar. When the other end port is multi-rate adaptive, it will adapt to the highest rate achievable at both ends. As a result, the module can be flexibly utilized in a variety of Ethernet environments.

Figure 1 Marvell AQR113C Solution Multi-Rate Compatibility Block Diagram

▪ The network cable interface supports 10GBase-T 10G rate, and the transmission distance is up to 30m via Cat 6A cable.

▪ The network interface supports 5GBase-T 5G rate with a transmission distance of up to 70m over Cat 5E cable.

▪ The network interface supports 2.5GBase-T 2.5G rate, and the transmission distance is up to 100m via Cat 5E cable.

▪ The network interface supports 10/100/1000Base-T rate, and the transmission distance is up to 100m via Cat 5E cable.

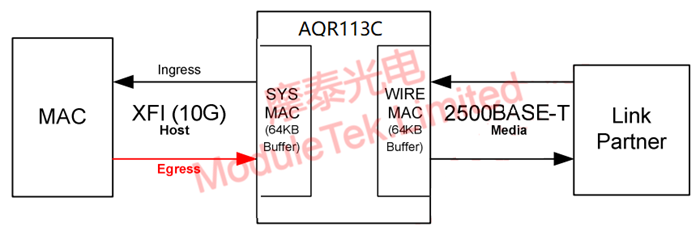

3. Flow Control

The AQR113C has an internal MACSec function. The main function of MACSec is to perform network security control, and it also has a flow control function, as shown in Figure 2 below. There is a 64KB buffer on both sides of the chip (host-side and cable-side), which can be used to perform integrity checks (ICVs), and also sends out pause frames according to the depth of the buffer fill.

When the module operates at 10G rate, the rate on both sides of the chip (host side and network line side) is 10G, there is no rate conversion and the bandwidth can be maintained at 10G.

When the cable side adapts to a rate below 10G, the host side is still working at 10G rate, at this time, the rate of both sides of the chip is not consistent, so the chip needs to be converted to the internal rate. The following 2.5G rate as an example of how the chip is flow control.

Figure 2 AQR113C program flow control block diagram

In the receiving direction, AQR113C receives the data sent from the other end at a rate of 2.5G, and AQR113C sends it to the host MAC at a rate of 10G, the receiving rate is much lower than the sending rate, so there is no frame overflow.

In the sending direction, the host MAC sends to the AQR113C at a rate of 10G, and the AQR113C sends to the opposite end at a rate of 2.5G, so the 64KB buffer fills up very quickly, and before it fills up, the PHY SYSMAC sends a pause frame to the host MAC, telling the host MAC to pause sending the data to the AQR113C, and wait until the buffer is almost empty, the SYSMAC then requests the host MAC to continue sending data. This will not result in frame overflow, ensuring that data transmission proceeds normally and that the bandwidth stabilizes at 2.5G.

Regarding the timing for SYSMAC to tell the host MAC to pause and restart data transmission, it can be set according to the upper and lower limits of buffer data filling, please refer to the datasheet of AQR113C for specific operation.

Moduletek Limited AQR113C solution 10GbE SFP module has stable performance and favorable price.

If you have any questions about the above content, you can contact us by Email : web@moduletek.com

40G/100G Optical Transceivers

40G/100G Optical Transceivers 10G/25G Optical Transceivers

10G/25G Optical Transceivers 155M/622M/2.5G Optical Transceivers

155M/622M/2.5G Optical Transceivers 100M/1G Optical Transceivers

100M/1G Optical Transceivers FC 16G/32G Optical Transceivers

FC 16G/32G Optical Transceivers CWDM/DWDM Optical Transceivers

CWDM/DWDM Optical Transceivers 100M/1G/10G Coppers

100M/1G/10G Coppers Active Cable AOC

Active Cable AOC Direct Attach Cable DAC

Direct Attach Cable DAC Regular/MTP-MPO Fiber Patch Cords

Regular/MTP-MPO Fiber Patch Cords MT2011

MT2011 MT2010

MT2010 CodingBox

CodingBox